# TECHNOLOGY TRADE-OFFS WHAT'S THE COST IMPACT OF:

- Additional RDL layers?

- Higher costs, better yield?

- Increasing TSV Count?

- Interposer versus true 3D?

## COST BREAKDOWN SUMMARIZE TOTAL COST

- Results are broken down into FEOL, BEOL, TSV creation and assembly.

- Wafer cost and unit cost are presented separately.

- Risk and yield are included in the total cost.

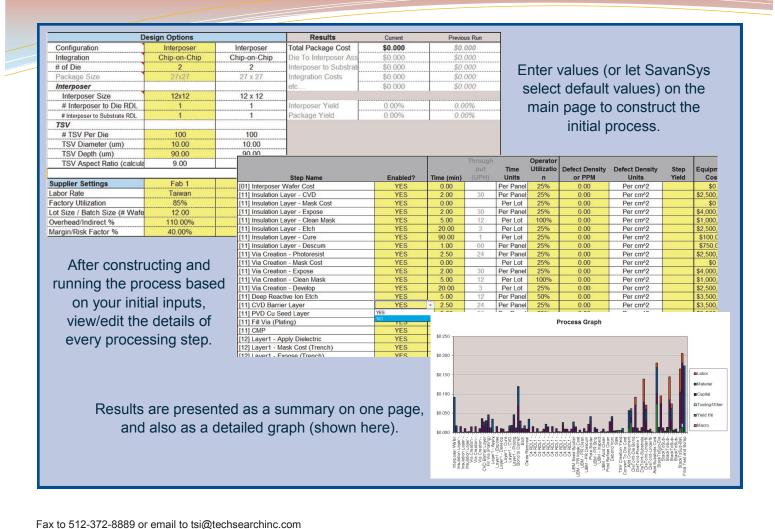

## PROCESS DETAILS COMPLETELY CUSTOMIZABLE

- Disable specific process steps.

- · Account for test activities.

- Customize process steps with known data (equipment cost, throughput, material, and more).

### **SUPPLIER SPECIFICS**

An optional enhancement is to create a model calibrated to your particular technology or to a specific supplier (internal or external). Ask us for more details.

## 2.5D & 3D Packaging Cost Model

Which applications are right for this technology?

This is the first cost model to cover the total cost and yield from fabrication of the wafer to complete assembly, for both 2.5D and 3D applications. Many detailed parameters are available for editing, but only a few inputs are required to run the analysis. For parameters you choose not to edit yourself, complex SavanSys algorithms automatically assign default values based on your other entries and extensive, up-to-date industry knowledge.

### Use the model to:

- Compare the cost of 2.5D and 3D packaging to see what makes sense for your product.

- Include supplier specific details and incoming die preparation in your analysis.

- View the detailed costs—including labor, material, capital, tooling, and yield impacts—for every step.

### Sample parameter list:

#### Design

2.5D process flow (chip-onchip/wafer/substrate) Number of Die Interposer size Number of RDL TSV Aspect Ratio Number of TSV per Die

#### **Preparation of Die**

Incoming Wafer Cost Location/Labor Rate Die Size

#### **Supplier Settings**

Labor rate Lot size Overhead rate Margin/Risk factor Factory utilization

### Advanced

TSV formation process type TSV formation yield RDL creation process type Underfill process ....and more

This model is the result of a joint project between TechSearch International, Inc., the leading market research firm in semiconductor packaging and assembly trends, and SavanSys Solutions LLC, the leader in electronic manufacturing cost modeling.

SavanSys Solutions LLC 10409 Peonia Ct. Austin, TX 78733 Tel: 512-402-9943 info@ savansys.com • www.savansys.com

TechSearch International 4801 Spicewood Springs Road • Suite 150 Austin, TX 78759 Tel: 512-372-8887 • Fax: 512-372-8889 tsi@techsearchinc.com • www.techsearchinc.com